- Главная

- Разное

- Образование

- Спорт

- Естествознание

- Природоведение

- Религиоведение

- Французский язык

- Черчение

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, фоны, картинки для презентаций

- Экология

- Экономика

Презентация, доклад по информатике на темуЛогические основы построения компьютера

Содержание

- 1. Презентация по информатике на темуЛогические основы построения компьютера

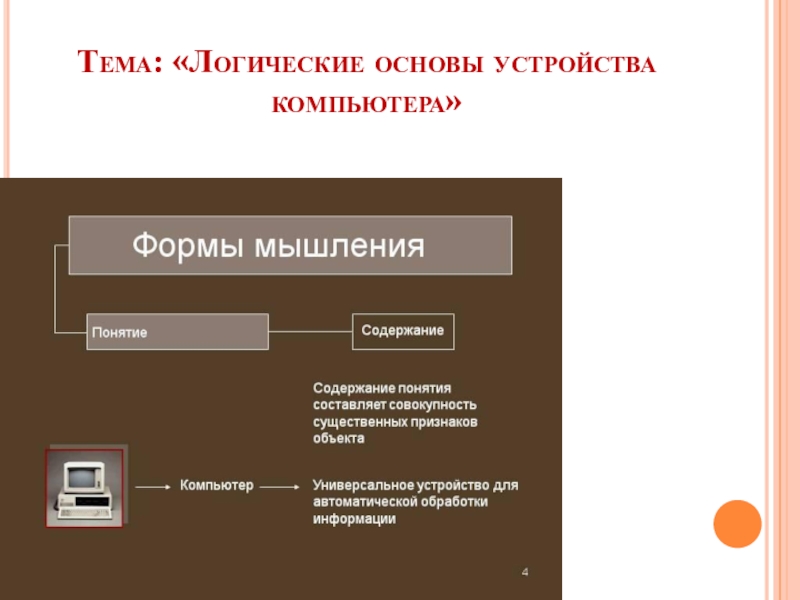

- 2. Тема: «Логические основы устройства компьютера»

- 3. План:Базовые логические элементыЛогический элемент «И»-логическое умножениеЛогический элемент

- 4. Базовые логические элементыБазовые логические элементы реализуют рассмотренные

- 5. Логический элемент «И»На входы А и В

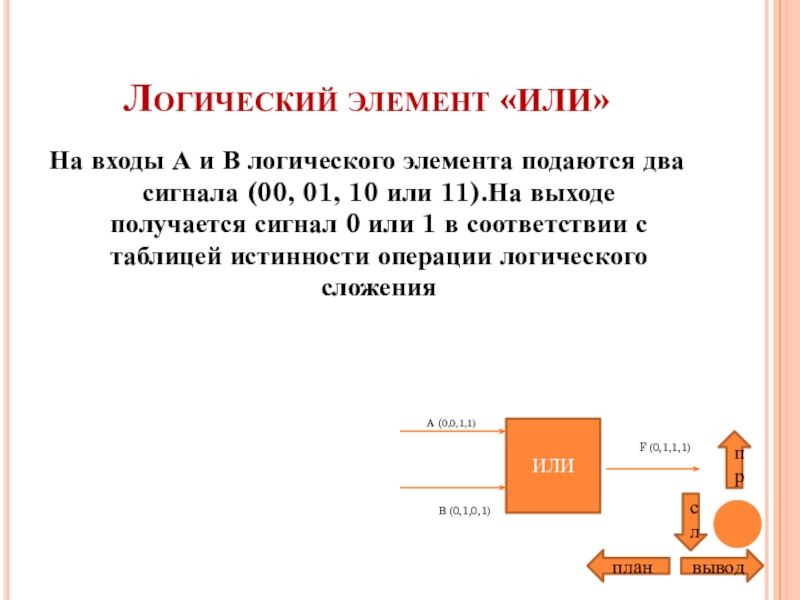

- 6. Логический элемент «ИЛИ»На входы А и В

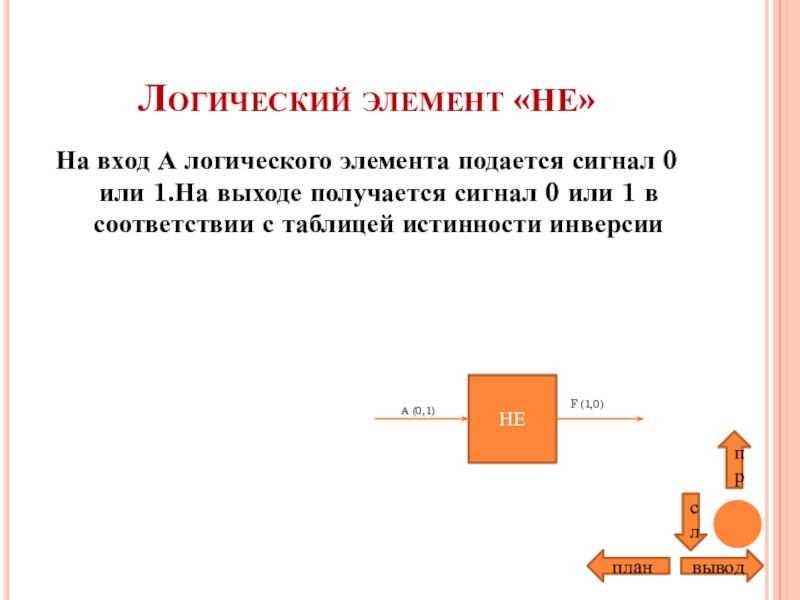

- 7. Логический элемент «НЕ»На вход А логического элемента

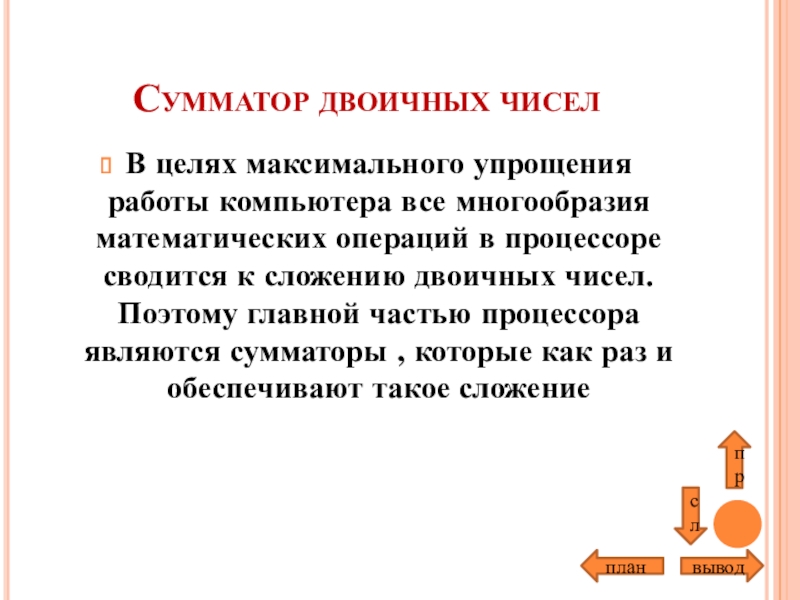

- 8. Сумматор двоичных чиселВ целях максимального упрощения работы

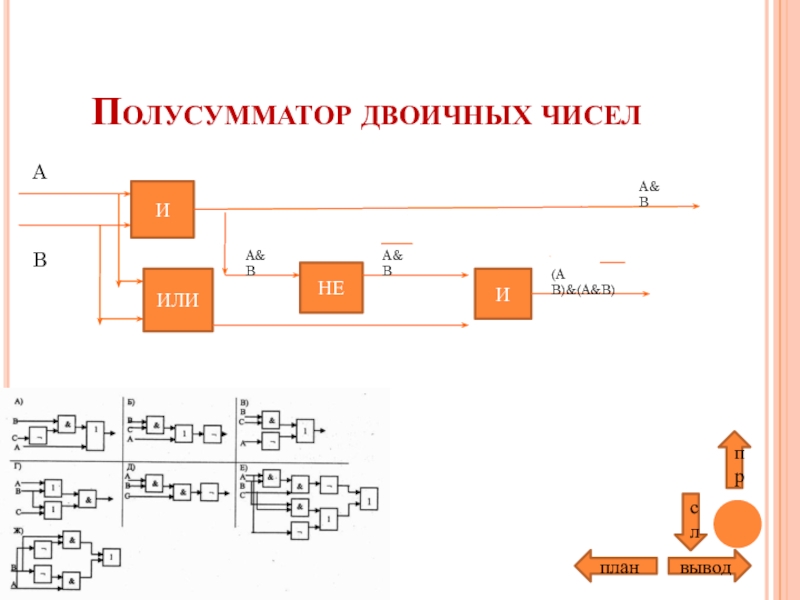

- 9. Полусумматор двоичных чиселИИЛИНЕИABA&BA&BA&B(A B)&(A&B)слпрпланвывод

- 10. Полный одноразрядный сумматорПолный одноразрядный сумматор должен иметь

- 11. Формула для вычисления суммы Форма переноса получает

- 12. Многоразрядный сумматорМногоразрядный сумматор процессора состоит из полных

- 13. ТриггерИЛИНЕИЛИНЕS(1)101001RQВ обычном состоянии на выходы триггера подан

- 14. ВыводВ данной работе рассмотрены особенности логических основ устройства компьютерапрплан

Слайд 1Презентация

Выполнено обучающимся группы №23 «Электромонтер по ремонту и обслуживанию электрооборудования»

Исаковым.Д.К

Преподаватель :

Слайд 3План:

Базовые логические элементы

Логический элемент «И»-логическое умножение

Логический элемент «ИЛИ»-логическое сложение

Логический элемент «НЕ»-инверсию

Сумматор

Полусумматор

Полный одноразрядный сумматор

Многоразрядный сумматор

Формула для вычисления суммы

Триггер

Вывод

Слайд 4Базовые логические элементы

Базовые логические элементы реализуют рассмотренные выше три основные логические

Логический элемент «И»-логическое умножение

Логический элемент «ИЛИ»-логическое сложение

Логический элемент «НЕ»-инверсию

сл

план

вывод

Слайд 5Логический элемент «И»

На входы А и В логического элемента подаются два

А (0,0,1,1)

В (0,1,0,1)

И

F(0,0,0,1)

сл

пр

план

вывод

Слайд 6Логический элемент «ИЛИ»

На входы А и В логического элемента подаются два

ИЛИ

А (0,0,1,1)

В (0,1,0,1)

F (0,1,1,1)

сл

пр

план

вывод

Слайд 7Логический элемент «НЕ»

На вход А логического элемента подается сигнал 0 или

НЕ

А (0,1)

F (1,0)

сл

пр

план

вывод

Слайд 8Сумматор двоичных чисел

В целях максимального упрощения работы компьютера все многообразия математических

сл

пр

план

вывод

Слайд 10Полный одноразрядный сумматор

Полный одноразрядный сумматор должен иметь три выхода: A ,

сл

пр

план

вывод

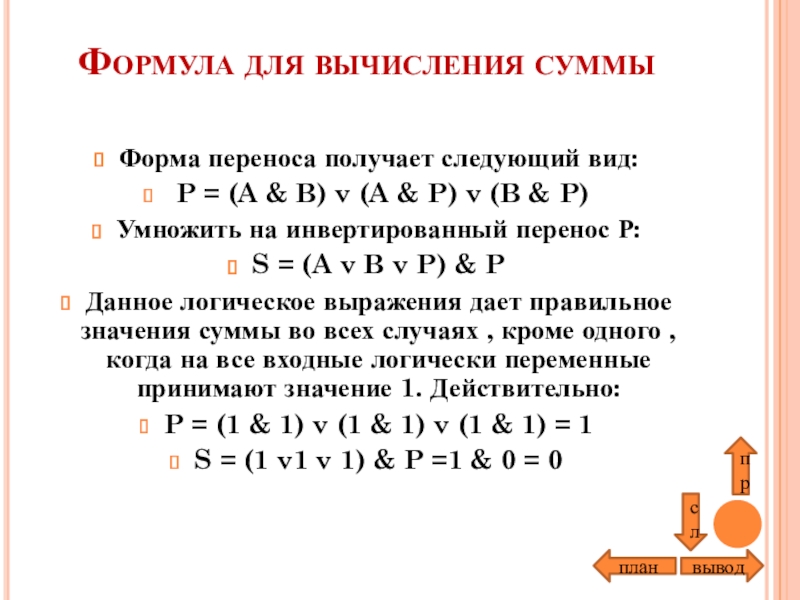

Слайд 11Формула для вычисления суммы

Форма переноса получает следующий вид:

P = (A

Умножить на инвертированный перенос Р:

S = (A v B v P) & P

Данное логическое выражения дает правильное значения суммы во всех случаях , кроме одного , когда на все входные логически переменные принимают значение 1. Действительно:

P = (1 & 1) v (1 & 1) v (1 & 1) = 1

S = (1 v1 v 1) & P =1 & 0 = 0

сл

пр

план

вывод

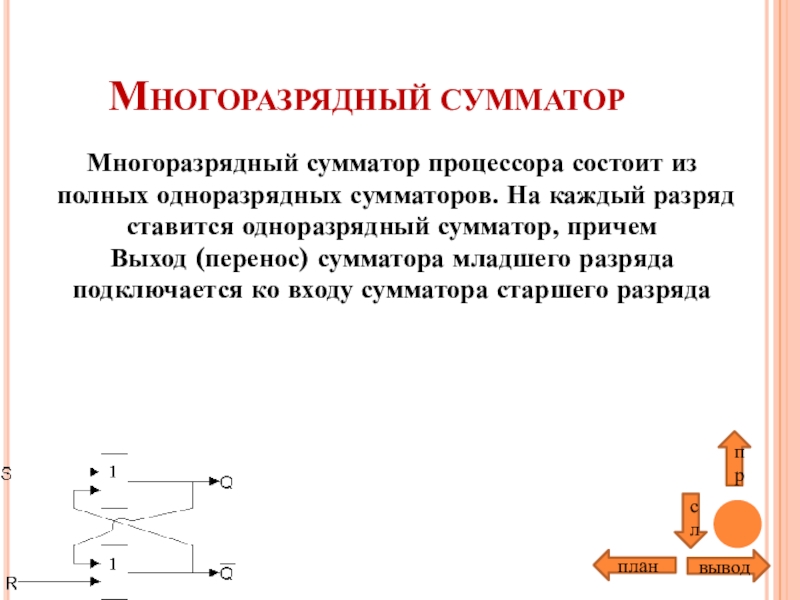

Слайд 12Многоразрядный сумматор

Многоразрядный сумматор процессора состоит из полных одноразрядных сумматоров. На каждый

Выход (перенос) сумматора младшего разряда подключается ко входу сумматора старшего разряда

сл

пр

план

вывод

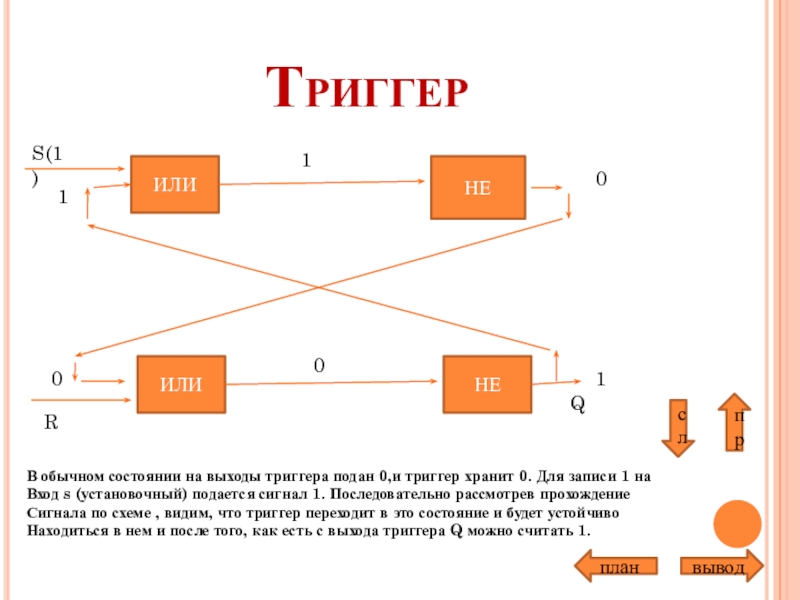

Слайд 13Триггер

ИЛИ

НЕ

ИЛИ

НЕ

S(1)

1

0

1

0

0

1

R

Q

В обычном состоянии на выходы триггера подан 0,и триггер хранит 0.

Вход s (установочный) подается сигнал 1. Последовательно рассмотрев прохождение

Сигнала по схеме , видим, что триггер переходит в это состояние и будет устойчиво

Находиться в нем и после того, как есть с выхода триггера Q можно считать 1.

сл

пр

план

вывод